# Digital Electronics and Computer Organization

Dr. Babasaheb Ambedkar Open University

# **Digital Electronics and**Computer Organization

# Course Writer:

Ms.Khyati Shah

Assistant Professor,

Som-Lalit Institute of Computer Applications

# **Content Reviewer and Editor:**

Prof. (Dr.) Nilesh K. Modi

Professor & Director School of Computer Science,

Dr. BabasahebAmbedkar Open University

Copyright © Dr. BabasahebAmbedkar Open University – Ahmedabad. 2024

# **ISBN No:**

Printed and published by: Dr. BabasahebAmbedkar Open University, Ahmedabad While all efforts have been made by editors to check accuracy of the content, the representation of facts, principles, descriptions and methods are that of the respective module writers. Views expressed in the publication are that of the authors, and do not necessarily reflect the views of Dr. BabasahebAmbedkar Open University. All products and services mentioned are owned by their respective copyrights holders, and mere presentation in the publication does not mean endorsement by Dr. BabasahebAmbedkar Open University. Every effort has been made to acknowledge and attribute all sources of information used in preparation of this learning material. Readers are requested to kindly notify missing attribution, if any

# Digital Electronics and Computer Organization

# BLOCK-1: DIGITAL COMPUTER AND DATA REPRESENTATION

| UNIT-1 DIGITAL COMPUTER                                        | 07    |

|----------------------------------------------------------------|-------|

| UNIT-2 DATA REPRESENTATION AND CONVERSIONS                     | 18    |

| UNIT-3<br>COMPLEMENTS                                          | 30    |

| UNIT-4<br>CODES                                                | 39    |

| BLOCK-2: LOGIC CIRCUITS, COMPONENT DIGITAL COMPUTER AND MEMORY | TS OF |

| UNIT-5 DIGITAL LOGIC CIRCUIT                                   | 48    |

| UNIT-6 COMPONENTS OF DIGITAL COMPUTER                          | 70    |

| UNIT-7<br>MEMORY                                               | 91    |

| UNIT-8 BUS AND MEMORY TRANSFER                                 | 99    |

| <b>BLOCK-3: CPU DESIGN AND INSTRUCTION</b> | SET     |

|--------------------------------------------|---------|

|                                            |         |

| UNIT-9                                     | 440     |

| REGISTER TRANSFER AND MICROOPERATION       | 110     |

| UNIT-10                                    |         |

| ARITHMETIC MICRO OPERATIONS                | 118     |

| UNIT-11                                    |         |

| BASIC COMPUTER ORGANIZATION                | 123     |

| DASIC COMITOTER ORGANIZATION               | 125     |

| UNIT-12                                    |         |

| CENTRAL PROCESSING UNIT                    | 130     |

| BLOCK-4: ORGANIZATION OF INPUT- OUTF       | PUT AND |

| MEMORY                                     |         |

|                                            |         |

| UNIT-13                                    |         |

| INPUT-OUTPUT ORGANIZATION                  | 148     |

| LINUT 49                                   |         |

| UNIT-13 MEMORY ORGANIZATION                | 153     |

| IVIEIVIORI ORGANIZATION                    | 103     |

|                                            |         |

# **Digital Electronics**

## Contents

#### BLOCK1: DIGITAL COMPUTER AND DATA REPRESENTATION

#### UNIT1 DIGITAL COMPUTER

Digital Computer, Types of signals, Hardware and Software, Computer Oraganisation, Von Neumann Architecture, Summary

#### UNIT2 DATA REPRESENTATION AND CONVERSIONS

Number System, Number System conversion, Floating Point Numbers, Normalization of Floating Point Numbers, Binary Addition, Binary Subtraction, Summary

#### UNIT3 COMPLEMENTS

Signed binary number, (r-1)'s Complement, (r)'s Complement, Subtraction using 1's Complement, Subtraction using 2's Complement, Summary

#### UNIT 4 CODES

Binary codes, BCD code, Excess-3 code, GRAY code, Alphanumeric codes, Summary

# BLOCK 2: LOGIC CIRCUITS, COMPONENTS OF DIGITAL COMPUTER AND MEMORY

#### UNIT5 DIGITAL LOGIC CIRCUIT

Logic Gates, Boolean Algebra, Boolean Function, Integrated Circuits, Combinational circuit(Half Adder and Full Adder), Flip-flops(SR, JK,D and T), Summary

# UNIT 6 COMPONENTS OF DIGITAL COMPUTER

Encoder, Decoder, Multiplexer, Registers, Shift Registers, Binary Counters, Summary

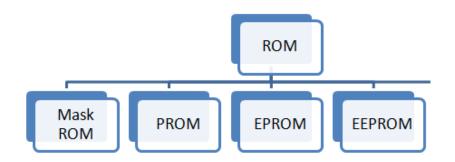

#### UNIT7 MEMORY

Memory Unit, Internal Structure of Memory Unit, Random Access Memory, Read only Memory, Types of Read Only Memory, Summary

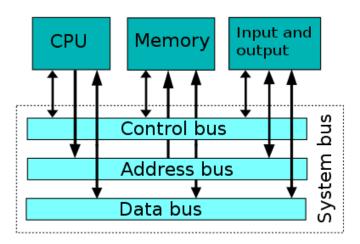

# UNIT 8 BUS AND MEMORY TRANSFER

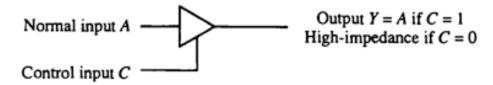

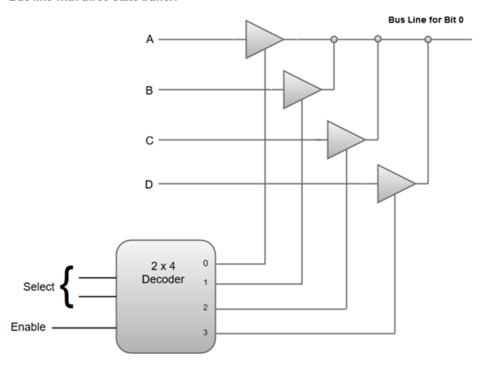

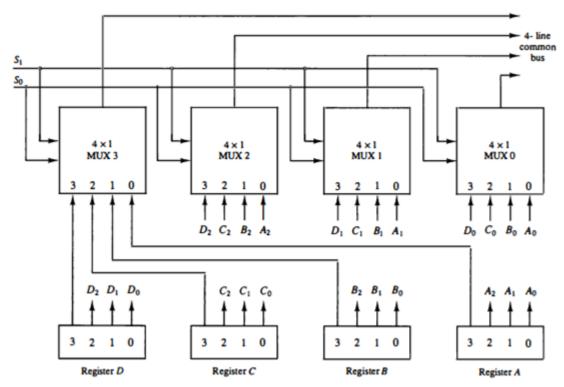

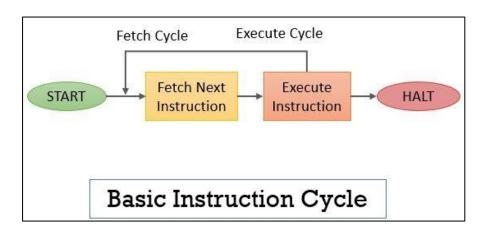

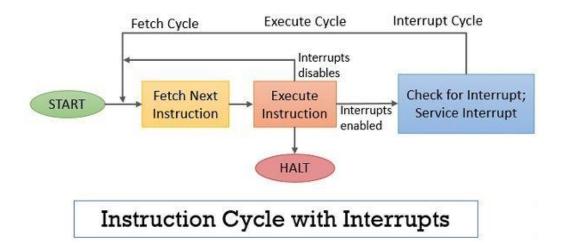

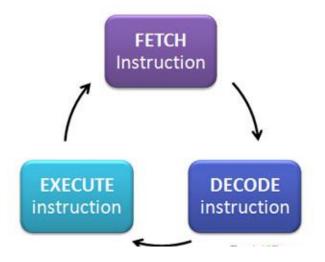

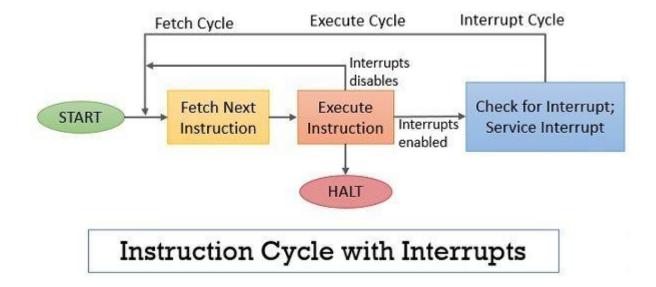

Concept of BUS ,Three-state buffer,Memory Transfer, Instruction Execution, Interrupt, Summary

#### **BLOCK 3: CPU DESIGN AND INSTRUCTION SET**

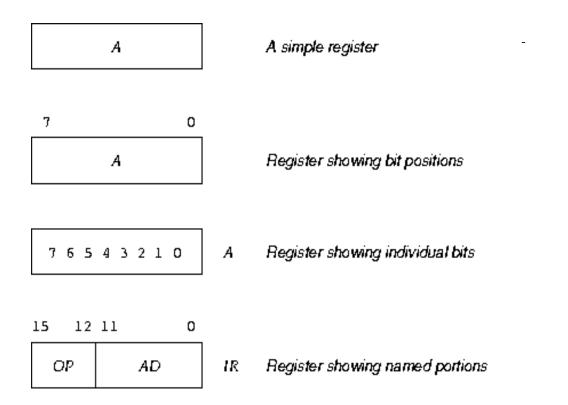

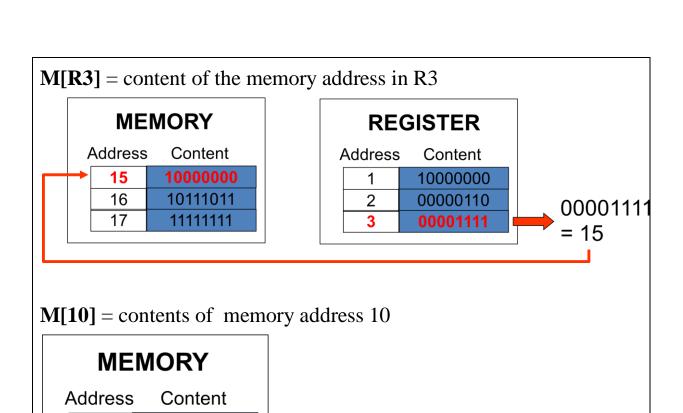

#### UNIT9 REGISTER TRANSFER AND MICROOPERATION

Register Transfer Language, Memory Read Operation, Memory Write Operation, Micro operations, Summary

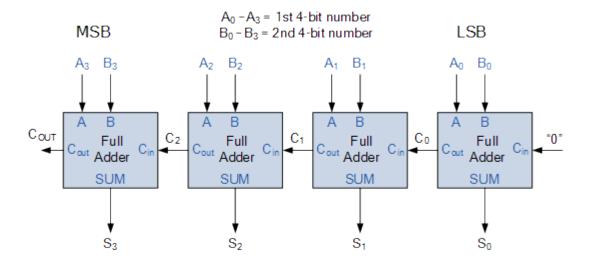

#### UNIT 10 ARITHMETIC MICRO OPERATIONS

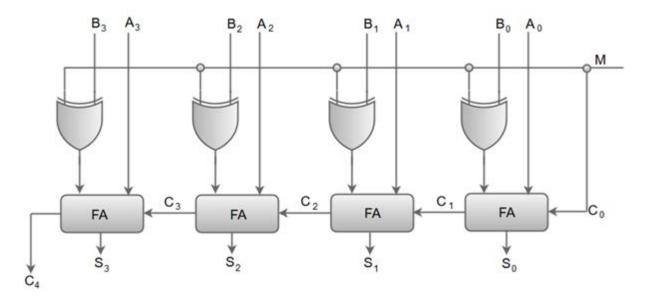

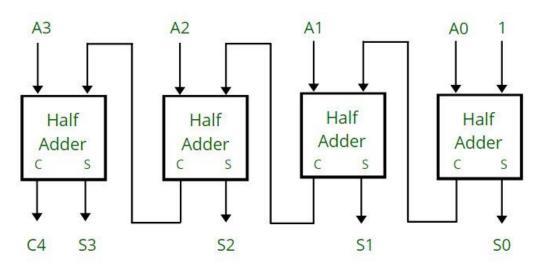

Introduction, Binary Adder, Binary Adder-Subtractor, Binary Incrementer, Summary

# UNIT11 BASIC COMPUTER ORGANIZATION

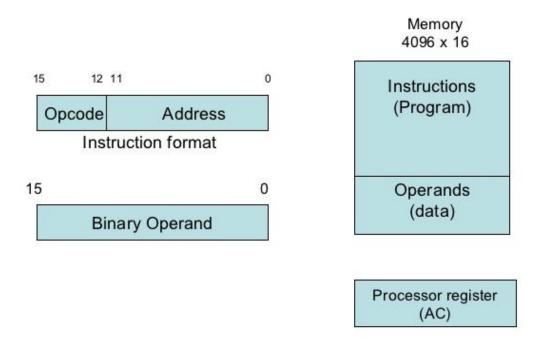

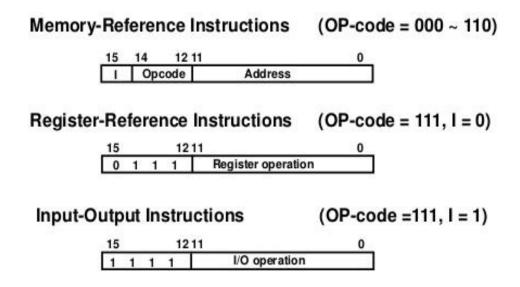

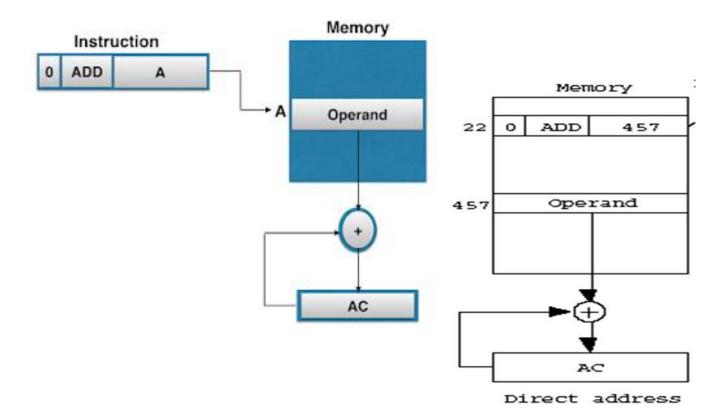

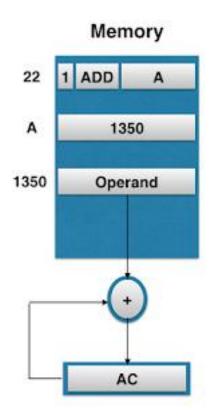

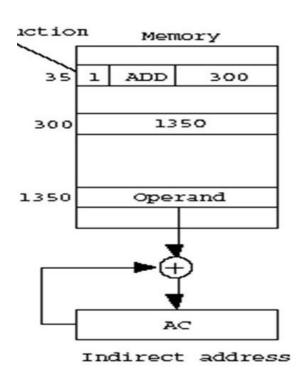

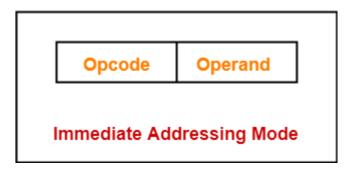

Instruction Code, Basic Computer Instructions ,Addressing, Instruction Cycle, Summary

#### UNIT12 CENTRAL PROCESSING UNIT

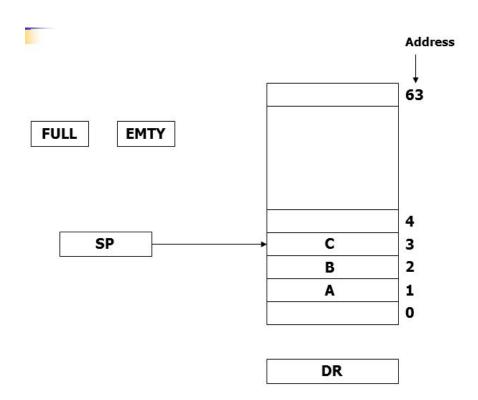

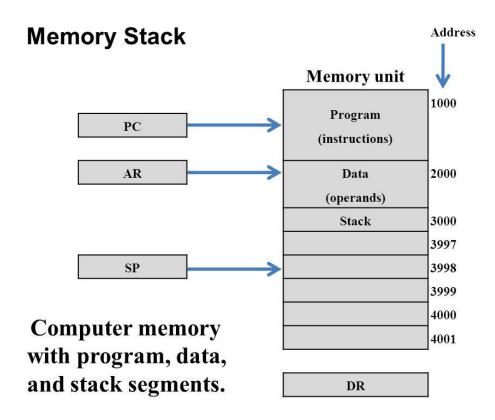

Introduction, Stack Organization, Addressing Modes, Program Interrupt, Summary

#### **BLOCK 4: ORGANIZATION OF INPUT- OUTPUT AND MEMORY**

#### UNIT13 INPUT-OUTPUT ORGANIZATION

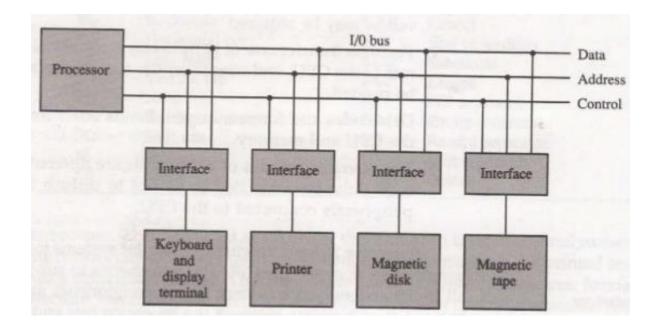

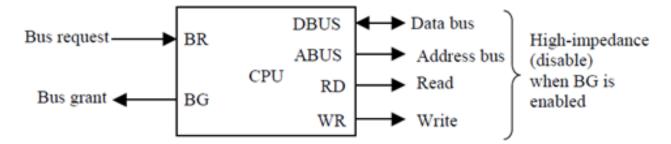

Peripheral devices, Input-Output Interface, DMA, Summary

#### **UNIT14** MEMORY ORGANIZATION

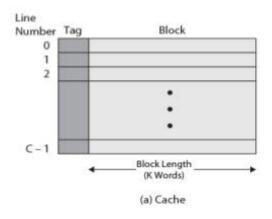

Memory Hierarchy, Main Memory, Auxiliary Memory, Cache Memory, Virtual Memory, Summary

# BLOCK 1: DIGITAL COMPUTER AND DATA REPRESENTATION

# **Block Introduction**

In this block-1 of Digital Electronics,I have emphasis on What is digital computer?,Types of signals, About hardware and software, instruction execution and interrupt.Basically, I introduced digital computer and how the hardware and software coordinates to perform instruction execution.I also described about interrupts and types of interrupt to understand instruction execution more Precisely.These will add better understanding about entire instruction execution cycle.

I have also emphasis on various number system and conversion between one number system to another number system. I tried to add also complements and codes for understanding of number system more betterly.

# **Block Objective**

The objective of the block is to explain what is digital computer and how request for instruction execution is given by use is handle. Detailed study of computer organization is requied to understand the working of computer.

By learning this block of digital electronics student will learn about computer organization, concept of BUS, instruction execution cycle. Reader of this block, will know about working of computer inernally.

Students also learn various number system and conversion between one number system to another number systemBy adding complements and codes for understanding of number system more betterly.

# **Unit 1: DIGITAL COMPUTER**

# **Unit Structure**

- 1.1. Digital Computer

- 1.2. Signals in Digital Computer

- 1.3. Hardware and Software

- 1.4. Computer Oraganisation

- 1.5. Von Neumann Architecture

- 1.6. Summary

# 1.1 Digital Computer

# **Digital**

A computer that performs calculations and logical operations with quantities represented as digits, usually in the binary number system.

A computer that accepts and processes data that has been converted into binary numbers.

The first electronic digital computers, developed in late 1940s, were used primarily for numerical computations.

#### Bit

A bit is short for binary digit and is a single unit of information that can have a value of either 0 or 1.A bit is represented by a lowercase b

All instructions that the computer executes and the data that it processes is made up of a group of bits.

Information is represented in digital computers in groups of bits. By using various coding techniques, groups of bits can be made to represent not only binary numbers but also other discrete symbols, such as decimal digits or letters of the alphabet.

Another unit of data representing eight bits is an octet. An octet always consists of eight bits, no matter the architecture.

# **Byte**

A byte is a storage unit capable of representing a single character, such as a letter, number or symbol. Technically speaking, a byte is a sequence of binary bits in a serialized data stream in data transmission systems. Byte is abbreviated with an uppercase B.

# How many bits in a byte?

In most computers, one byte is equated to eight smaller units called bits, although the size of a byte has always been dependent on hardware.

# Types of bytes

While bytes are measured in bit multiples, computer storage is typically measured in byte multiples. Due to massive increases in storage capacity over time, there are now eight additional units of measurement following the byte. The eight different

types of bytes currently used in computer architectures range from kilobytes (1,024 bytes) to yottabytes (1,024 zettabytes).

Byte multiples can be measured using two systems: base-2 or base-10. A base-2, or binary, system is commonly expressed as a rounded off decimal number.

**Note:** One kibibyte contains 1,024 bytes. One mebibyte contains 1,024 x 1,024 or 1,048,576 bytes.

# **Program**

A sequence of instructions for the computer is called a program.

The data that are manipulated by the program constitute the database.

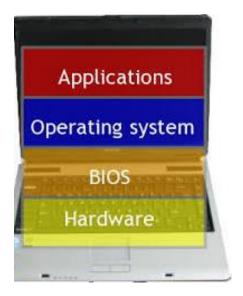

# **Layers in Modern Computer**

A modern computer is collection of different multiple layers. Shown in below diagram.

#### **Hardware**

The inner most layer is hardware surrounded by system software and application software.

# **BIOS (Basic Input-Output System)**

The BIOS or basic input-output system of a computer provides the computer with some of its most basic capabilities.

A computer can use the BIOS to start and perform some very basic functions even without an operating system installed.

One of the most important things the BIOS do is load the operating system when the computer is started.

It also manages the various devices connected to the computer, and acts as a sort of 'traffic cop' to direct instructions and data to the appropriate layers and components of the computer's architecture.

# **Operating System**

The operating system controls the capabilities of the computer's hardware. In particular, the operating system carries out these responsibilities:

- 1. Processor management identifying and prioritizing (scheduling) task

- 2. **Memory management** managing flow of data in and out of RAM, managing virtual memory as needed

- 3. Device management providing the interface between devices and the CPU

- Storage management managing permanent storage on hard drives and other media

- Application Interface managing communications between applications and the computer

- **6. User Interface** managing interactions with the user allowing them to control the computer

# 1.2 | Signals in Digital Computer

# What is a Signal?

A signal is an electrical or electromagnetic current that is used to transfer data from one network to another.

There are two types of signals which are used in computer networking,

- 1. Analog signals

- 2. Digital signals

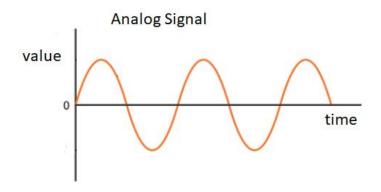

# 1. Analog Signals

These are the signals which can have an infinite number of different magnitude or values. They vary continuously with time. They are generated by signal generations hardware.

# **Examples of Analog Devices and Computers**

- Speedometer

- Tide Predictor

- Thermometer

- Analog clock

- Nomogram: a graphical calculating device

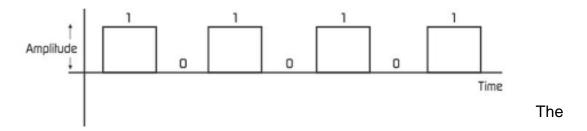

# 2. Digital signals

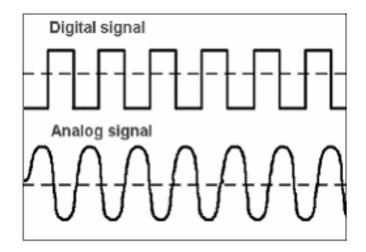

The signal, whose amplitude takes only limited values is called Digital signal. Digital signal are discrete, they contain only distinct values.

Digital signals carry binary data i.e. 0 or 1 in form of bits, it can only contain one value at a period of time. Digital signals are represented as square waves or clock signals.

Binary signals are examples of digital signals

following diagram shows the diagrammatic comparison of the digital and analog signals.

# **Analog and Digital Signal Difference**

The following table shows the analog and digital signals difference in computer networking.

| Analog Signal                                                                           | Digital Signal                                                 |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|

| It uses a continuous range of values to represent information.                          | Digital signal uses discrete signals to represent information. |

| The bandwidth of the analog signal is low.                                              | The bandwidth of a digital signal is high.                     |

| There is no fixed range in analog signals.                                              | Digital signal has a finite range, i.e. 0 and 1                |

| It is denoted by sine waves, as shown in the above diagram.                             | It is denoted by square waves as shown in the above diagram    |

| Analog signals are used in temperature sensors, FM radio, photocells and light sensors. | Digital signals are used in computers, DVDs and CDs            |

# 1.3 Hardware and Software

# **Hardware**

Hardware is the physical parts of computer.

Hardware refers to the physical elements of a computer. This is also sometime called the machinery or the equipment of the computer. Examples of hardware in a computer are the keyboard, the monitor, the mouse and the processing unit.

A computer's hardware is comprised of many different parts, but perhaps the most important of these is the motherboard. The motherboard is made up of even more parts that power and control the computer.

#### **Software**

Software is the electronic instructions that tell the computer to perform a task.

Software, commonly known as programs, consists of all the electronic instructions that tell the hardware how to perform a task.

These instructions come from a software developer in the form that will be accepted by the platform (operating system + CPU) that they are based on

Computer systems divide software systems into **two major classes**:

- 1) **System software:** Helps run computer hardware and computer system itself. System software includes operating systems, device drivers, diagnostic tools and more. System software is almost always pre-installed on your computer.

- Application software: Allows users to accomplish one or more tasks. Includes word processing, web browsing and almost any other task for which you might install software. (Some application software is pre-installed on most computer systems.)

#### **Difference between Application Software System Software**

|             | Application Software                                                                           | System Software                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Definition  | Application software is computer software designed to help the user to perform specific tasks. | System software is computer software designed to operate the computer hardware and to provide a platform for running application software. |

| Purpose     | It is specific purpose software.                                                               | It is general-purpose software.                                                                                                            |

| Environment | Application Software performs in a environment which created by System/Operating System        | System Software Create his own environment to run itself and run other application.                                                        |

| Execution Time | It executes as and when required.                                     | It executes all the time in computer.                                                                                         |

|----------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Essentiality   | Application software is not essential for a computer to work.         | System software is essential for a computer to work. Without System software (like operating systems), a computer is useless. |

| Number         | The number of application software is much more than system software. | The number of system software is less than application software.                                                              |

| Example        | Examples are: Windows, Dos, Unix, Linux, Norton Antivirus etc.        | Examples are: MS Word, MS Excel, MS Power point etc.                                                                          |

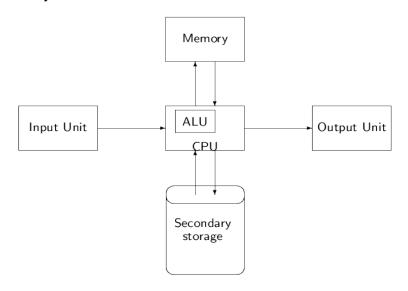

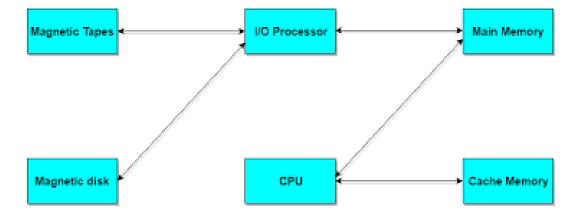

# 1.4 Computer Organisation

The basic design of a computer includes how different parts of computer are organized and how various operations are performed between different parts of computer to do a specific task.

A computer has five functionally independent main parts:

- Input Unit

- Arithmetic and logic Unit

- Control unit

- Output Unit

- Memory Unit

# **Input Device**

Computers accept coded information through input units, which read the data.

The most well-known input device is keyboard. Whenever a key is pressed, the corresponding letter or digit is automatically translated into its corresponding binary code and transmitted over a cable to either the memory or the processor.

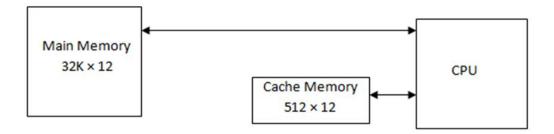

# **Memory Unit**

The function of the memory unit is to store programs and data.

There are two classes of storage, called primary and secondary.

- Primary storage is a fast memory that operates at electronic speeds. Programs must be stored in the memory while they are being executed.

- Memory in which any location can be reached in a short and fixed amount of time after specifying its address is called Random Access Memory (RAM).

- Secondary storage is used when large amounts of data and many programs have to be stored, particularly for information that is accessed infrequently. Ex:magnetic disks and tapes and optical disks.

Difference between Primary Memory and Secondary Memory

|               | Primary Memory(main<br>Memory)                      | Secondary<br>Memory(auxiliary<br>Memory)                     |  |  |

|---------------|-----------------------------------------------------|--------------------------------------------------------------|--|--|

| Volatility    | This is volatile.                                   | This is Non-volatile.                                        |  |  |

| Access Time   | Access Time is higher Than Secondary memories.      | Access Time is lower Than Primary memories.                  |  |  |

| Memory Status | This is a Temporary Memory.                         | This is a Permanent Memory.                                  |  |  |

| Capacity      | At present time, 512 MB to 8 GB RAMs are available. | At Present time 80 GB to 4 TB Hard Disc Drive are available. |  |  |

| Price         | Higher than HDD/Secondary Memory                    | Lower Than primary Memory.                                   |  |  |

| Connection    | Connected via Slots.                                | Connected Via Cables.                                        |  |  |

| Accessible    | Primary memory is directly accessible to the CPU    | Secondary memory is not directly accessible to the CPU       |  |  |

| Speed         | It is relatively fast memory.                       | It is slow in compare to main memory.                        |  |  |

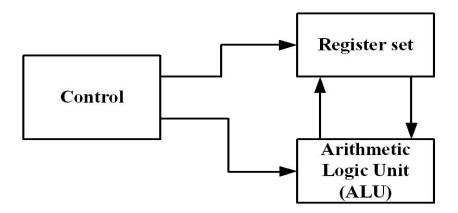

# **Arithmetic and Logic Unit**

All the arithmetic or logic operation is initiated by bringing the required operands into the processor, where the operation is performed by the ALU.

# **Control Unit**

The Control Unit is used to co-ordinate the operations of memory, ALU, input and output units.

The Control Unit determines the sequence in which computer programs and instructions are executed.

# **Output Unit**

Its function is to send processed result to the outside world. Ex:- Printer.

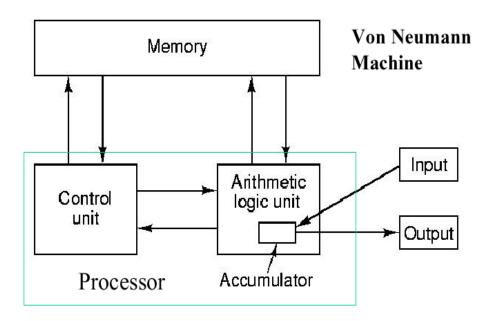

# 1.5 Von Neumann Architecture

Von Neumann Architecture is comprised of the five classical components (input, output, processor, memory).

The processor is divided into an arithmetic logic unit (ALU) and control unit. Within the processor, the ALU data path mediates data transfer for computation.

A Von Neumann Architecture computer performs following sequence of steps and computer repeatedly performs the following cycle of events.

- 1. Fetch an instruction from memory.

- 2. Fetch any data required by the instruction from memory.

- 3. Execute the instruction (process the data).

- 4. Store results in memory.

- 5. Go back to step (1).

Von Neumann computers spend a lot of time moving data to and from the memory, and this slows the computer. This is called the von Neumann bottleneck.

# 1.9 Summary

In this chapter you have learned about:

- Digital Computer

- Signals in Digital Computer

- Hardware and Software

- Computer Oraganisation

- Von Neumann Architecture

# Unit 2: Data Representation and Conversions

# **Unit Structure**

- 2.1. Number System

- 2.2. Number System Conversion

- 2.3. Floating Point Numbers

- 2.4. Normalization of Floating Point Numbers

- 2.5. Binary Addition

- 2.6. Binary Subtraction

- 2.7. Summary

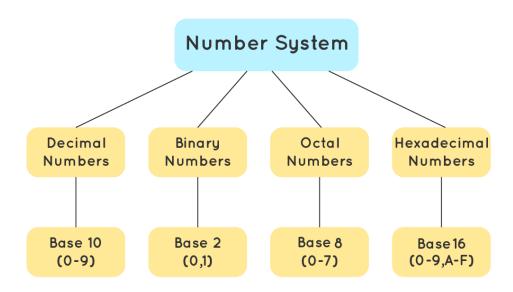

# 2.1 Number System

#### **Definition**

A number system is defined as the representation of numbers by using digits or other symbols in a consistent manner. The value of any digit in a number can be determined by a digit, its position in the number, and the base of the number system. The numbers are represented in a unique manner and allow us to operate arithmetic operations like addition, subtraction, and division.

# **Types of Number Systems**

There are different types of number systems in which the four main types are:

- Decimal number system (Base 10)

- Binary number system (Base 2)

- Octal number system (Base 8)

- Hexadecimal number system (Base 16)

# **Decimal Number System**

The decimal number system consists of 10 digits 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9 and is the most commonly used number system. We use the combination of these 10 digits to form all other numbers. The value of a digit in a number depends upon its position in the number.

The decimal number system is the system that we generally use to represent numbers in real life. If any number is represented without a base, it means that its base is 10. For example: 723<sub>10</sub>, 32<sub>10</sub>, 4257<sub>10</sub> are some examples of numbers in the decimal number system.

# **Binary Number System**

The binary number system uses only two digits: 0 and 1. It means a 2 number system. The numbers in this system have a base of 2. Digits 0 and 1 are called bits and 8 bits together make a byte.

For example: 10001<sub>2</sub>, 111101<sub>2</sub>, 1010101<sub>2</sub> are some examples of numbers in the binary number system.

# Representation of a Binary Number

| MSB |     |                       | E                     | Binary Dig | it         |    |    | LSB |

|-----|-----|-----------------------|-----------------------|------------|------------|----|----|-----|

| 28  | 27  | <b>2</b> <sup>6</sup> | <b>2</b> <sup>5</sup> | 24         | <b>2</b> ³ | 22 | 21 | 2º  |

| 256 | 128 | 64                    | 32                    | 16         | 8          | 4  | 2  | 1   |

# **Octal Number System**

The octal number system uses eight digits: 0,1,2,3,4,5,6 and 7 with the base of 8. The advantage of this system is that it has lesser digits when compared to several other systems, hence, there would be fewer computational errors. Digits like 8 and 9 are not included in the octal number system.

For example: 35<sub>8</sub>, 23<sub>8</sub>, 141<sub>8</sub> are some examples of numbers in the octal number system.

# **Hexadecimal Number System**

The word hexadecimal comes from Hexa meaning 6, and decimal meaning 10. So, in a hexadecimal number system, there are 16 digits. In the hex system, the numbers are first represented just like in the decimal system, i.e. from 0 to 9. Then, the numbers are represented using the alphabet from A to F.

| Hexadecimal | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | Α  | В  | С  | D  | E  | F  |

|-------------|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| Decimal     | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

# 2.2 Number System Conversion

Numbers can be represented in any of the number system categories like binary, decimal, hex, etc. Also, any number which is represented in any of the number system types can be easily converted to other.

The conversion of one base number to another base number considering all the base numbers such as decimal, binary, octal and hexadecimal with the help of examples. Here, the following number system conversion methods are explained.

- Binary to Decimal Number System

- Decimal to Binary Number System

- Octal to Binary Number System

- Binary to Octal Number System

- Binary to Hexadecimal Number System

- Hexadecimal to Binary Number System

# **Number System Conversion Table**

| Binary Numbers | Octal Numbers | Decimal Numbers | Hexadecimal<br>Numbers |

|----------------|---------------|-----------------|------------------------|

| 0000           | 0             | 0               | 0                      |

| 0001           | 1             | 1               | 1                      |

| 0010           | 2             | 2               | 2                      |

| 0011           | 3             | 3               | 3                      |

| 0100           | 4             | 4               | 4                      |

| 0101           | 5             | 5               | 5                      |

| 0110           | 6             | 6               | 6                      |

| 0111           | 7             | 7               | 7                      |

| 1000           | 10            | 8               | 8                      |

| 1001           | 11            | 9               | 9                      |

| 1010           | 12            | 10              | А                      |

| 1011           | 13            | 11              | В                      |

| 1100           | 14            | 12              | С                      |

| 1101           | 15            | 13              | D                      |

| 1110           | 16            | 14              | E                      |

| 1111           | 17            | 15              | F                      |

# **Number System Conversion Methods**

Number system conversions deal with the operations to change the base of the numbers. For example, to change a decimal number with base 10 to binary number with base 2. We can also perform the arithmetic operations like addition, subtraction, multiplication on the number system.

The methods to convert the number of one base to the number of another base starting with the decimal number system. The representation of number system base conversion in general form for any base number is;

$$(Number)_b = d_{n-1} d_{n-2} - d_1 d_0 \cdot d_{-1} d_{-2} - d_{-m}$$

In the above expression,  $d_{n-1} d_{n-2}$ —.  $d_1 d_0$  represents the value of integer part and  $d_1 d_{-2}$ ——  $d_{-m}$  represents the fractional part.

Also,  $d_{n-1}$  is the Most significant bit (MSB) and  $d_{-m}$  is the Least significant bit (LSB).

# **Decimal to Other Bases**

Converting a decimal number to other base numbers is easy. We have to divide the decimal number by the converted value of the new base.

# **Decimal to Binary Number:**

Suppose if we have to convert decimal to binary, then divide the decimal number by 2.

**Example 1.** Convert (25)<sub>10</sub> to binary number.

| Operation | Output | Remainder |

|-----------|--------|-----------|

| 25 ÷ 2    | 12     | 1(MSB)    |

| 12 ÷ 2`   | 6      | 0         |

| 6 ÷ 2     | 3      | 0         |

| 3 ÷ 2     | 1      | 1         |

| 1 ÷ 2     | 0      | 1(LSB)    |

Therefore, from the above table, we can write,

$$(25)_{10} = (11001)_2$$

#### **Decimal to Octal Number:**

To convert decimal to octal number we have to divide the given original number by 8 such that base 10 changes to base 8. Let us understand with the help of an example.

**Example 2:**Convert 128<sub>10</sub> to octal number.

| Operation | Output | Remainder |

|-----------|--------|-----------|

| 128÷8     | 16     | 0(MSB)    |

| 16÷8      | 2      | 0         |

| 2÷8       | 0      | 2(LSB)    |

Therefore, the equivalent octal number = 2008

#### **Decimal to Hexadecimal:**

Again in decimal to hex conversion, we have to divide the given decimal number by 16.

# Example 3:Convert 128<sub>10</sub> to hex.

| Operation | Output | Remainder |

|-----------|--------|-----------|

| 128÷16    | 8      | 0(MSB)    |

| 8÷16      | 0      | 8(LSB)    |

Therefore, the equivalent hexadecimal number is 80<sub>16</sub>

Here MSB stands for a Most significant bit and LSB stands for a least significant bit.

# Other Base System to Decimal Conversion

# **Binary to Decimal**

In this conversion, binary number to a decimal number, we use multiplication method, in such a way that, if a number with base n has to be converted into a number with base 10, then each digit of the given number is multiplied from MSB to LSB with reducing the power of the base. Let us understand this conversion with the help of an example.

**Example 1.** Convert (1101)<sub>2</sub> into a decimal number.

**Solution:** Given a binary number (1101)<sub>2</sub>.

Now, multiplying each digit from MSB to LSB with reducing the power of the base number 2.

$$1 \times 2^{3} + 1 \times 2^{2} + 0 \times 2^{1} + 1 \times 2^{0}$$

=  $8 + 4 + 0 + 1$

=  $13$

Therefore,  $(1101)_2 = (13)_{10}$

#### Octal to Decimal:

To convert octal to decimal, we multiply the digits of octal number with decreasing power of the base number 8, starting from MSB to LSB and then add them all together.

# Example 2: Convert 22<sub>8</sub> to decimal number.

Solution: Given, 228

$$2 \times 8^{1} + 2 \times 8^{0}$$

$$= 16 + 2$$

= 18

Therefore,  $22_8 = 18_{10}$

# **Hexadecimal to Decimal:**

Example 3: Convert 121<sub>16</sub> to decimal number.

Solution:  $1 \times 16^2 + 2 \times 16^1 + 1 \times 16^0$

$$= 16 \times 16 + 2 \times 16 + 1 \times 1$$

= 289

Therefore,  $121_{16} = 289_{10}$

# **Hexadecimal to Binary Shortcut Method**

To convert hexadecimal numbers to binary and vice versa is easy, you just have to memorize the table given below.

| Hexadecimal Number | Binary |

|--------------------|--------|

| 0                  | 0000   |

| 1                  | 0001   |

| 2                  | 0010   |

| 3                  | 0011   |

| 4                  | 0100   |

| 5                  | 0101   |

| 6                  | 0110   |

| 7                  | 0111   |

| 8                  | 1000   |

| 9                  | 1001   |

| A                  | 1010   |

| В                  | 1011   |

| С                  | 1100   |

| D                  | 1101   |

| E                  | 1110   |

| F                  | 1111   |

You can easily solve the problems based on hexadecimal and binary conversions with the help of this table. Let us take an example.

**Example:** Convert (89)<sub>16</sub> into a binary number.

**Solution:** From the table, we can get the binary value of 8 and 9, hexadecimal base numbers.

8 = 1000 and 9 = 1001

Therefore,  $(89)_{16} = (10001001)_2$

# **Octal to Binary Shortcut Method**

To convert octal to binary number, we can simply use the table. Just like having a table for hexadecimal and its equivalent binary, in the same way, we have a table for octal and its equivalent binary number.

| Octal Number | Binary |

|--------------|--------|

| 0            | 000    |

| 1            | 001    |

| 2            | 010    |

| 3            | 011    |

| 4            | 100    |

| 5            | 101    |

| 6            | 110    |

| 7            | 111    |

**Example:** Convert (214)<sub>8</sub> into a binary number.

Solution: From the table, we know,

$2 \rightarrow 010$

$1 \rightarrow 001$

$4 \rightarrow 100$

Therefore,  $(214)_8 = (010001100)_2$

# **Practice Problems on Number System Conversion**

- 1. Convert 146<sub>10</sub> into a binary number system

- 2. Convert 1A7<sub>16</sub> into the decimal number system

- 3. Convert (110010)<sub>2</sub> into octal number system

- 4. Convert DA2<sub>16</sub> into the binary number system

- 5. Convert 4652<sub>8</sub> into the binary number system

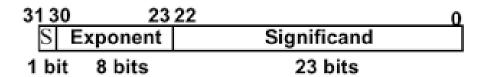

# 2.3 Floating Point Numbers

Floating point numbers are numbers that contain floating decimal points.

A floating-point number is one where the position of the decimal point can "float" rather than being in a fixed position within a number.

Examples of floating-point numbers are 1.23, 87.425, and 6.5 etc. Different programming languages or systems may have different size limits or ways of defining floating-point numbers

# **Storing Floating Point**

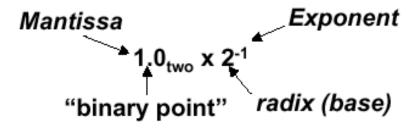

We split a Floating Point number into sign, exponent and mantissa as in the following diagram showing 23 bits for the mantissa ,8 bits for the exponent and 1 bit for sign bit:

# Example

# 2.4 Normalization of Floating Point Numbers

Before a floating-point binary number can be stored correctly, its mantissa must be normalized.

The process is basically the same as when normalizing a floating-point decimal number. For example, decimal 1234.567 is normalized as 1.234567 x 103 by moving the decimal point so that only one digit appears before the decimal.

The exponent expresses the number of positions the decimal point was moved left (positive exponent) or moved right (negative exponent).

Similarly, the floating-point binary value 1101.101 is normalized as  $1.101101 \times 23$  by moving the decimal point 3 positions to the left, and multiplying by 23. Here are some examples of normalizations:

| Binary Value | Normalized As | Exponent |

|--------------|---------------|----------|

| 1101.101     | 1.101101      | 3        |

| .00101       | 1.01          | -3       |

| 1.0001       | 1.0001        | 0        |

| 10000011.0   | 1.0000011     | 7        |

# 2.5 Binary Addition

Binary addition is one of the binary operations. The binary addition operation works similarly to the base 10 decimal system, except that it is a base 2 system. The binary system consists of only two digits, 1 and 0. Most of the functionalities of the computer system use the binary number system.

# **Rules of Binary Addition**

| Case | А | + | В | Sum | Carry |

|------|---|---|---|-----|-------|

| 1    | 0 | + | 0 | 0   | 0     |

| 2    | 0 | + | 1 | 1   | 0     |

| 3    | 1 | + | 0 | 1   | 0     |

| 4    | 1 | + | 1 | 0   | 1     |

In fourth case, a binary addition is creating a sum of (1 + 1 = 10) i.e. 0 is written in the given column and a carry of 1 over to the next column.

# **Example – Addition**

# 2.6 Binary Subtraction

Binary subtraction is one of the four binary operations, where we perform the subtraction method for two binary numbers (comprising only two digits, 0 and 1)

There are four rules of binary subtraction.

| А | В | Difference | Borrow |

|---|---|------------|--------|

| 0 | 0 | 0          | 0      |

| 0 | 1 | 1          | 1      |

| 1 | 0 | 1          | 0      |

| 1 | 1 | 0          | 0      |

when we subtract one from zero, we must borrow one from the next higher order digit to lower the digit by one, and the residual number left here is likewise 1.

# **Example – Subtraction**

# 2.7 Summary

In this chapter you have learned about:

- Number System

- Number System Conversion

- Floating Point Numbers

- Normalization of Floating Point Numbers

- Binary Addition

- Binary Subtraction

# **UNIT 3: COMPLEMENTS**

# **Unit Structure**

- 3.1. Signed binary number

- 3.2. Complements of number

- 3.3. Subtraction using 1's Complement

- 3.4. Subtraction using 2's Complement

- 3.5. Summary

# 3.1 | Signed binary number

# **Representation of Binary Numbers:**

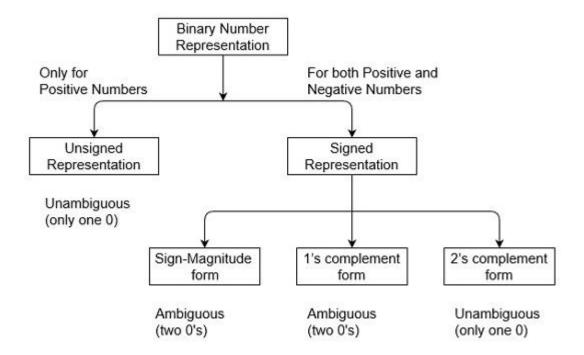

Binary numbers can be represented in signed and unsigned way. Unsigned binary numbers do not have sign bit.

whereas signed binary numbers uses signed bit as well or these can be distinguishable between positive and negative numbers. A signed binary is a specific data type of a signed variable.

There are three types of representations for signed binary numbers. Because of extra signed bit, binary number zero has two representation, either positive (0) or negative (1) These are:

- 1. Sign-Magnitude form

- 2. 1's complement form

- 3. 2's complement form

# 3.2 Complements of Numbers

In a number system, there is a fixed range of numbers and when you pick any number from the system, you have a complement for that number in the number system.

# **Types of Complements**

There are two types of complements.

- 1. r-1's complement or Diminished Radix Complement.

- 2. r's complement or Radix Complement.

# 1. r-1's complement or Diminished Radix Complement

The (r-1)'s complement of a number in any number system with base r can be found out by subtracting every single digit of a number by r-1.

Suppose a number N is given

N = Number

r = base of the number

n = Number of digits in the number.

The r-1's complement of the number is given by the formula.

$$(r^{n} - 1) - N$$

# **Examples**

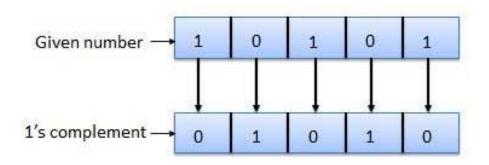

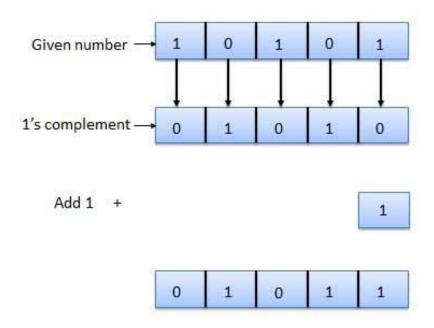

# I. 1's complement

The 1's complement of a number is found by changing all 1's to 0's and all 0's to 1's. This is called as taking complement or 1's complement. Example of 1's Complement is as follows.

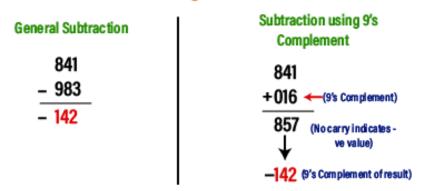

# II. 9's Complement

The 9's complement is used to find the subtraction of the decimal numbers.

The 9's complement of a number is calculated by subtracting each digit of the number by 9.

**For example**, suppose we have a number 1423, and we want to find the 9's complement of the number. For this, we subtract each digit of the number 1423 by 9. So, the 9's complement of the number 1423 is 9999-1423= 8576.

There are two possible cases when we subtract the numbers using 9's complement.

a) For subtracting the smaller number from the larger number using 9's complement, calculate 9's complement of smaller number or negative number, and by adding complement and first number, the result will come in the formation of carry. At last, we will add this carry to the result obtained previously.

# When subtrahend is smaller than the minuend

b) For subtracting the larger number from the smaller number using 9's complement, calculate 9's complement of negative number, and by adding complement and first number, than no carry is generated than result is negative and make 9's complement of result and put negative sign.

# When subtrahend is greater than the minuend

# 2. r's complement or Radix Complement

The r's complement of a non-zero number in any number system with base r can be calculated by adding 1 to the LSB of its (r-1)'s complement.

To find radix complement of a number N where

N = Number

r. = base of the number

n = Number of digits in the number.

The r's complement of the number is given as

$$rn - N$$

or  $r-1$ 's complement + 1 => [(  $rn - 1$ ) -  $N$ ] + 1

# **Examples**

# I. 2's complement

The 2's complement of binary number is obtained by adding 1 to the Least Significant Bit (LSB) of 1's complement of the number.

2's complement = 1's complement + 1

Example of 2's Complement is as follows.

# II. 10's Complement

The 10's complement is used to find the subtraction of the decimal numbers.

The 10's complement of a number is calculated by subtracting each digit by 9 and then adding 1 to the result. Simply, by adding 1 to its 9's complement we can get its 10's complement value.

For example, suppose we have a number 1423, and we want to find the 10's complement of the number. For this, we find the 9's complement of the number 1423 that is 9999-1423= 8576, and now we will add 1 to the result. So the 10's complement of the number 1423 is 8576+1=8577.

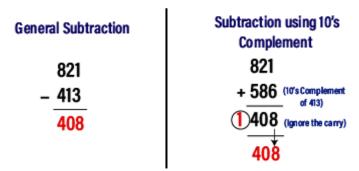

There are **two possible cases** when we subtract the numbers using 10's complement.

a) For subtracting the smaller number from the larger number using 10's complement, calculate 10's complement of smaller number or negative number, and by adding complement and first number, the result will come in the formation of carry, then ignore carry.

### When subtrahend is smaller than the minuend

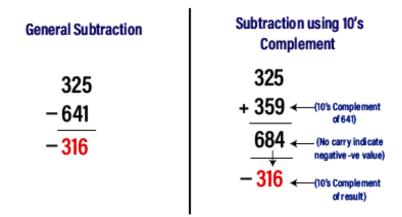

b) For subtracting the larger number from the smaller number using 10's complement, first calculate 10's complement of negative number, and by adding complement and first number, than no carry is generated than result is negative and make 10's complement of result and put negative sign.

### When subtrahend is smaller than the minuend

# 3.3 Subtraction using 1's Complement

These are the following steps to subtract two binary numbers using 1's complement

- o In the first step, find the 1's complement of the subtrahend(negative number).

- Next, add the complement number with the minuend(first number).

- If got a carry, add the carry to its LSB.

- If carry is not generated than take 1's complement of the result which will be negative

#### Example 1: 10101 - 00111

We take 1's complement of subtrahend 00111, which comes out 11000. Now, sum them. So,

10101+11000 =1 01101.

In the above result, we get the carry bit 1, so add this to the LSB of a given result, i.e., 01101+1=01110, which is the answer.

#### Example 2: 10101 - 10111

We take 1's complement of subtrahend 10111, which comes out 01000. Now, add both of the numbers. So,

10101+01000 =11101.

In the above result, we didn't get the carry bit. So calculate the 1's complement of the result, i.e., 00010, which is the negative number and the final answer.

# 3.4 Subtraction using 2's Complement

These are the following steps to subtract two binary numbers using 2's complement

- o In the first step, find the 2's complement of the subtrahend.

- Add the complement number with the minuend.

- If we get the carry by adding both the numbers, then we discard this carry and the result is positive

- If carry is not generated than take 2's complement of the result which will be negative.

#### **Example 1:** 10101 - 00111

We take 2's complement of subtrahend 00111, which is 11001. Now, sum them. So,

10101+11001=101110.

In the above result, we get the carry bit 1. So we discard this carry bit and remaining is the final result and a positive number.

#### **Example 2:** 10101 - 10111

We take 2's complement of subtrahend 10111, which comes out 01001. Now, we add both of the numbers. So,

10101+01001 =11110.

In the above result, we didn't get the carry bit. So calculate the 2's complement of the result, i.e., 00010. It is the negative number and the final answer.

# 3.9 Summary

In this chapter you have learned about:

- Signed binary number

- Complements of number

- Subtraction using 1's Complement

- Subtraction using 2's Complement

# **UNIT 4: CODES**

# **Unit Structure**

- 4.1. Binary code

- 4.2. Excess-3 code

- 4.3. GRAY code

- 4.4. Alphanumeric codes

- 4.5. Summary

# 4.1 Binary codes

The digital data is represented, stored and transmitted as group of bits. This group of bits is also called as **binary code**.

Binary codes can be classified into two types.

- 1. Weighted codes

- 2. Unweighted codes

If the code has positional weights, then it is said to be weighted code. Otherwise, it is an unweighted code.

#### 1) 8 4 2 1 code

The weights of this code are 8, 4, 2 and 1. This code has all positive weights. So, it is a positively weighted code.

This code is also called as natural BCD (Binary Coded Decimal) code.

| Decimal Digit | 8421 Code |

|---------------|-----------|

| 0             | 0000      |

| 1             | 0001      |

| 2             | 0010      |

| 3             | 0011      |

| 4             | 0100      |

| 5             | 0101      |

| 6             | 0110      |

| 7             | 0111      |

| 8             | 1000      |

#### 2) 2 4 2 1 code

The weights of this code are 2, 4, 2 and 1. This code has all positive weights. So, it is a positively weighted code.

It is an unnatural BCD code. Sum of weights of unnatural BCD codes is equal to 9.

It is a self-complementing code. Self-complementing codes provide the 9's complement of a decimal number, just by interchanging 1's and 0's in its equivalent 2421 representation.

| Decimal | 8421 | 2421 |

|---------|------|------|

| Digit   | Code | Code |

| 0       | 0000 | 0000 |

| 1       | 0001 | 0001 |

| 2       | 0010 | 0010 |

| 3       | 0011 | 0011 |

| 4       | 0100 | 0100 |

| 5       | 0101 | 1011 |

| 6       | 0110 | 1100 |

| 7       | 0111 | 1101 |

| 8       | 1000 | 1110 |

| 9       | 1001 | 1111 |

# 4.2 Excess-3 code

The Excess-3 code is nonweighted binary code. Following are steps to convert binary number to Excess-3 code.

#### **Steps**

- Step 1 -- Convert decimal to BCD.

- Step 2 -- Add (3)<sub>2</sub> to BCD number.

Example – convert (1001)<sub>BCD</sub> to Excess-3.

#### Step 1 - Convert to decimal

$9_{10=}(1001)_{BCD}$

#### Step 2 - Add 3 to decimal

$$(1001)_2 + (0011)_2 = (1100)_2$$

#### Step 3 - Convert to Excess-3

$$(1100)_2 = (12)_{10}$$

| Decimal | BCD     | Excess-3   |

|---------|---------|------------|

|         | 8 4 2 1 | BCD + 0011 |

| 0       | 0 0 0 0 | 0 0 1 1    |

| 1       | 0 0 0 1 | 0 1 0 0    |

| 2       | 0 0 1 0 | 0 1 0 1    |

| 3       | 0 0 1 1 | 0 1 1 0    |

| 4<br>5  | 0 1 0 0 | 0 1 1 1    |

| 5       | 0 1 0 1 | 1 0 0 0    |

| 6       | 0 1 1 0 | 1 0 0 1    |

| 7       | 0 1 1 1 | 1 0 1 0    |

| 8       | 1 0 0 0 | 1 0 1 1    |

| 9       | 1 0 0 1 | 1 1 0 0    |

### Table showing all three codes together

| Decimal Digit | 8421 Code | 2421 Code | Excess 3 Code |

|---------------|-----------|-----------|---------------|

| 0             | 0000      | 0000      | 0011          |

| 1             | 0001      | 0001      | 0100          |

| 2             | 0010      | 0010      | 0101          |

| 3             | 0011      | 0011      | 0110          |

| 4             | 0100      | 0100      | 0111          |

| 5             | 0101      | 1011      | 1000          |

| 6             | 0110      | 1100      | 1001          |

| 7             | 0111      | 1101      | 1010          |

| 8             | 1000      | 1110      | 1011          |

| 9             | 1001      | 1111      | 1100          |

# 4.3 GRAY code

It is a non-weighted code .Gray code is a coded binary representation of a decimal digit which has a change in 1-bit position for consecutive digits.

Gray code is a coded binary representation of a decimal digit which has a change in 1-bit position for consecutive digits.

Gray Code sequences have to be converted to Binary or Binary Coded Decimal (BCD) if they are used in mathematical computations or for displays.

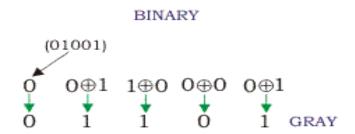

#### **Binary to Gray Code Conversion**

Steps given below elaborate on the idea on this type of conversion.

- 1. The M.S.B. of the gray code will be exactly equal to the first bit of the given binary number.

- 2. Now the second bit of the code will be exclusive-or of the first and second bit of the given binary number, i.eif both the bits are same the result will be 0 and if they are different the result will be 1.

- 3. The third bit of gray code will be equal to the exclusive-or of the second and third bit of the given binary number. Thus the Binary to gray code conversion goes on. One example given below can make your idea clear on this type of conversion.

Following table shows binary value and gray code value of decimal number.

| Decimal numbers | Binary code | Gray code |

|-----------------|-------------|-----------|

| 0               | 0000        | 0000      |

| 1               | 0001        | 0001      |

| 2               | 0010        | 0011      |

| 3               | 0011        | 0010      |

| 4               | 0100        | 0110      |

| 5               | 0101        | 0111      |

| 6               | 0110        | 0101      |

| 7               | 0111        | 0100      |

| 8               | 1000        | 1100      |

| 9               | 1001        | 1101      |

| 10              | 1010        | 1111      |

# 4.4 Alphanumeric codes

Alphanumeric codes are basically binary codes.

We can write alphanumeric data, including data, letters of the alphabet, numbers, mathematical symbols and punctuation marks by this code which can be easily understandable and can be processed by the computers.

The most common **alphanumeric codes** used these days are **ASCII code** and **EBCDIC code**.

#### 1. ASCII Code

The full form of **ASCII code** is American Standard Code for Information Interchange. It is a seven bit code based on the English alphabet.

ASCII code has 128 characters

#### 2. EBCDIC code

The EBCDIC stands for Extended Binary Coded Decimal Interchange Code.

EBCDIC is an IBM code for representing characters as numbers. Although it is widely used on large IBM computers, All the IBM computers and peripherals use this code. It is an 8 bit code and therefore can accommodate 256 characters

| Char | EBCDIC    |

|------|-----------|

| Α    | 1100 0001 |

| В    | 1100 0010 |

| С    | 1100 0011 |

| D    | 1100 0100 |

| E    | 1100 0101 |

| F    | 1100 0110 |

| G    | 1100 0111 |

| Н    | 1100 1000 |

|      | 1100 1001 |

# 4.5 Summary

In this chapter you have learned about:

- Binary code

- Excess-3 code

- GRAY code

- Alphanumeric codes

# BLOCK 2: LOGIC CIRCUITS, COMPONENTS OF DIGITAL COMPUTER AND MEMORY

#### **Block Introduction**

In this block-2 of digitasl electronics, I have tried to emphasis on: logic gates, components of digital computer and memory. Basically, I introduced concept of logic gates which helps in further circuit building. Along with this I have covered combinational circuits, flip-flops to understand how various operations are perform by various circuits in computer.

I hace also emphasis on registers, counters, internal structure and types of memory to understand how data is store and access from memory for any instruction.

#### **Block Objective**

The objective of the block is to explain logic gates which are building blocks for building any circuit. Students will able to learn about various circuits, flip-flops and meory.

By learning this block of digital electronics student will also learn about more details of how data is transfer between registers and memory . Reader of this block, will know about memory and memory transfer.

# **Unit 5: Digital Logic Circuit**

### **Unit Structure**

- 5.1. Logic Gates

- 5.2. Boolean Algebra

- 5.3. Boolean Function

- 5.4. Integrated Circuit

- 5.5. Combinational Circuit

- 5.6. Flip-flops

- 5.7. Summary

# 5.1 Logic Gates

#### **Definition**

Logic gates are the basic building blocks of any digital system.

It is an electronic circuit having one or more than one input and only one output. The relationship between the input and the output is based on certain logic.

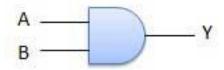

#### 1. AND Gate

A circuit which performs an AND operation is shown in figure. It has n input  $(n \ge 2)$  and one output.

The AND gate produces the AND logic function, that is, the output is 1 if input A and input B are both equal to 1; otherwise the output is 0. The algebraic symbol of the AND function is the same as the multiplication symbol

#### Logic diagram

#### **Truth Table**

| Inpu | ts | Output |

|------|----|--------|

| Α    | В  | AB     |

| 0    | 0  | 0      |

| 0    | 1  | 0      |

| 1    | 0  | 0      |

| 1    | 1  | 1      |

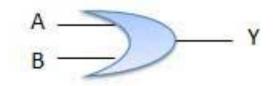

#### 2. OR Gate

A circuit which performs an OR operation is shown in figure. It has n input  $(n \ge 2)$  and one output.

The OR gate produces the inclusive-OR function; that is, the output is 1 if input A or input B or both inputs are 1; otherwise, the output is 0. The algebraic symbol of the OR function is +

#### Logic diagram

#### **Truth Table**

| Inpu | its | Output |

|------|-----|--------|

| Α    | В   | A + B  |

| 0    | 0   | 0      |

| 0    | 1   | 1      |

| 1    | 0   | 1      |

| 1    | 1   | 1      |

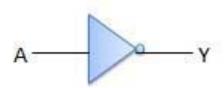

#### 3. NOT Gate

NOT gate is also known as Inverter. It has one input A and one output Y.

The inverter circuit inverts the logic sense of a binary signal. It produces the NOT, or complement, function.

The algebraic symbol used for the logic complement is a bar over the variable symbol.

$$Y$$

= NOT A  $\overline{A}$

#### Logic diagram

#### **Truth Table**

| Inputs | Output |

|--------|--------|

| Α      | В      |

| 0      | 1      |

| 1      | 0      |

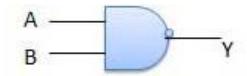

#### 4. NAND Gate

A NOT-AND operation is known as NAND operation. It has n input ( $n \ge 2$ ) and one output.

The NAND function is the complement of the AND function, as indicated by the graphic symbol, which consists of an AND graphic symbol followed by a small circle.

The designation NAND is derived from the abbreviation of NOT-AND.

#### Logic diagram

#### **Truth Table**

| Inpu | its | Output |

|------|-----|--------|

| Α    | В   | AB     |

| 0    | 0   | 1      |

| 0    | 1   | 1      |

| 1    | 0   | 1      |

| 1    | 1   | 0      |

#### 5. NOR Gate

A NOT-OR operation is known as NOR operation. It has n input ( $n \ge 2$ ) and one output.

The NOR gate is the complement of the OR gate and uses an OR graphic symbol followed by a small circle.

### Logic diagram

Truth Table

| Inpu | ts | Output |

|------|----|--------|

| Α    | В  | A+B    |

| 0    | 0  | 1      |

| 0    | 1  | 0      |

| 1    | 0  | 0      |

| 1    | 1  | 0      |

#### What are Universal Gates?

In Electronic physics there are AND, NOT and OR gates are the basic gates, we can create any logic gate or any Boolen expression by combining a mixture of these gates.

NOR gates and NAND gates have the particular property that any one of them can create any logical Boolen expression if appropriately designed so they are called a universal gate.

A universal gate is a logic gate which can implement any Boolean function without the need to use any other type of logic gate. The NOR gate and NAND gate are universal gates. This means that you can create any logical Boolean expression using only NOR gates or only NAND gates.

In practice, this is advantageous since NOR and NAND gates are economical and easier to fabricate than other logic gates.

#### 6. XOR Gate

XOR or Ex-OR gate is a special type of gate. It can be used in the half adder, full adder and subtractor. The exclusive-OR gate is abbreviated as EX-OR gate or sometime as X-OR gate. It has n input ( $n \ge 2$ ) and one output.

The exclusive-OR gate has a graphic symbol similar to the OR gate except for the additional curved line on the input side.

The output of the gate is 1 if any input is 1 but excludes the combination when both inputs are 1.

Y = A XOR B XOR C ...... N

Y = A

$$\bigoplus$$

B  $\bigoplus$  C ...... N

Y = AB + AB

Logic diagram

#### **Truth Table**

| Inpu | its | Output  |

|------|-----|---------|

| Α    | В   | A (+) B |

| 0    | 0   | 0       |

| 0    | 1   | 1       |

| 1    | 0   | 1       |

| 1    | 1   | 0       |

#### 7. XNOR Gate

XNOR gate is a special type of gate. It can be used in the half adder, full adder and subtractor. The exclusive-NOR gate is abbreviated as EX-NOR gate or sometime as X-NOR gate. It has n input (n >= 2) and one output.

The exclusive-NOR is the complement of the exclusive-OR, as indicated by the small circle in the graphic symbol.

The output of this gate is 1 only if both the inputs are equal to 1 or both inputs are equal to 0.

#### Logic diagram

#### **Truth Table**

| Inpu | its | Output |  |  |

|------|-----|--------|--|--|

| Α    | В   | A B    |  |  |

| 0    | 0   | 1      |  |  |

| 0    | 1   | 0      |  |  |

| 1    | 0   | 0      |  |  |

| 1    | 1   | 1      |  |  |

# 5.2 Boolean Algebra

Boolean algebra is used to analyze and simplify the digital (logic) circuits. It uses only the binary numbers i.e. 0 and 1. It is also called as Binary Algebra or logical Algebra.

Boolean algebra was invented by George Boole in 1854.

#### Rule in Boolean Algebra

Following are the important rules used in Boolean algebra.

- Variable used can have only two values. Binary 1 for HIGH and Binary 0 for LOW.

- Complement of a variable is represented by an overbar (-). Thus, complement of variable B is represented as B. Thus if B = 0 then B = 1 and B = 1 then B = 0.

- ORing of the variables is represented by a plus (+) sign between them. For example ORing of A, B, C is represented as A + B + C.

- Logical ANDing of the two or more variable is represented by writing a dot between them such as A.B.C. Sometime the dot may be omitted like ABC.

#### **Boolean Laws**

There are six types of Boolean Laws.

#### **Commutative law**

Any binary operation which satisfies the following expression is referred to as commutative operation.

(i)

$$A.B = B.A$$

(ii)  $A + B = B + A$

Commutative law states that changing the sequence of the variables does not have any effect on the output of a logic circuit.

#### **Associative law**

This law states that the order in which the logic operations are performed is irrelevant as their effect is the same.

(i)

$$(A.B).C = A.(B.C)$$

(ii)  $(A+B)+C=A+(B+C)$

#### **Distributive law**

Distributive law states the following condition.

$$A.(B+C) = A.B + A.C$$

#### **AND law**

These laws use the AND operation. Therefore they are called as AND laws.

(i)

$$A.0 = 0$$

(i)

$$A.0 = 0$$

(ii)  $A.1 = A$

(iii)

$$A.A = A$$

(iv)  $A.\overline{A} = 0$

(iv)

$$A.\overline{A} = 0$$

#### **OR law**

These laws use the OR operation. Therefore they are called as OR laws.

(i)

$$A + 0 = A$$

(ii)

$$A + 1 = 1$$

(i)

$$A + 0 = A$$

(ii)  $A + 1 = 1$

(iii)  $A + A = A$  (iv)  $A + \overline{A} = 1$

(iv)

$$A + \overline{A} = 1$$

#### Inversion law

This law uses the NOT operation. The inversion law states that double inversion of a variable results in the original variable itself.

$$\frac{=}{A} = A$$

### 1. Boolean Algebra simplification rules

| 1. $A + \overline{A} = 1$                              | 2.  A + A = A                                            |

|--------------------------------------------------------|----------------------------------------------------------|

| $3.  A \cdot A = A$                                    | $4. \qquad A \cdot \overline{A} = 0$                     |

| $5. A \cdot (B+C) = A \cdot B + A \cdot C$             | 6. $A + 0 = A$                                           |

| 7. $A+1=1$                                             | $8.  A \cdot 1 = A$                                      |

| $9.  A \cdot 0 = 0$                                    | 10. $A \cdot B = B \cdot A$                              |

| 11. $A + B = B + A$                                    | 12. $B \cdot (A + \overline{A}) = B$                     |

| $13.  A + A \cdot B = A$                               | <b>14.</b> $A \cdot (A + B) = A$                         |

| $15.  A + \overline{A} \cdot B = A + B$                | $16.  A \cdot (\overline{A} + B) = A \cdot B$            |

| 17. $\overline{A+B} = \overline{A} \cdot \overline{B}$ | 18. $\overline{A \cdot B} = \overline{A} + \overline{B}$ |

#### De Morgan's Theoram

De Morgan has suggested two theorems which are extremely useful in Boolean Algebra. The two theorems are discussed below.

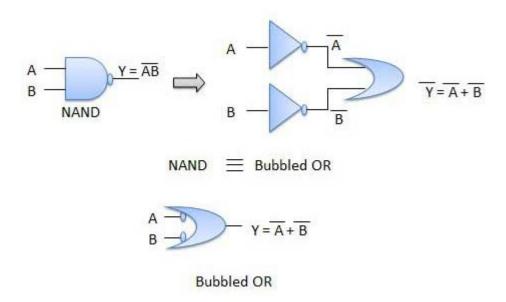

#### Theorem 1

$$\overline{A.B} = \overline{A} + \overline{B}$$

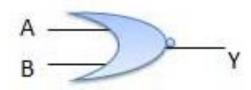

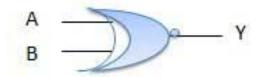

NAND = Bubbled OR

The left hand side (LHS) of this theorem represents a NAND gate with inputs A and B, whereas the right hand side (RHS) of the theorem represents an OR gate with inverted inputs.

This OR gate is called as Bubbled OR.

Table showing verification of the De Morgan's first theorem -

| Α | В | AB | Ā | B | $\overline{A} + \overline{B}$ |

|---|---|----|---|---|-------------------------------|

| 0 | 0 | 1  | 1 | 1 | 1                             |

| 0 | 1 | 1  | 1 | 0 | 1                             |

| 1 | 0 | 1  | 0 | 1 | 1                             |

| 1 | 1 | 0  | 0 | 0 | 0                             |

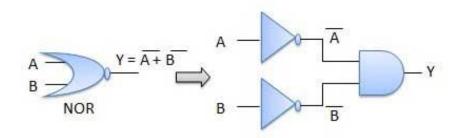

#### Theorem 2

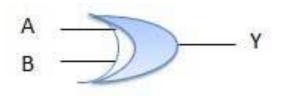

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

NOR = Bubbled AND

The LHS of this theorem represents a NOR gate with inputs A and B, whereas the RHS represents an AND gate with inverted inputs.

This AND gate is called as Bubbled AND.

NOR ≡ Bubbled AND

**Bubbled AND**

Table showing verification of the De Morgan's second theorem -

| A | В | A+B | Ā | B | Ā.B |

|---|---|-----|---|---|-----|

| 0 | 0 | 1   | 1 | 1 | 1   |

| 0 | 1 | 0   | 1 | 0 | 0   |

| 1 | 0 | 0   | 0 | 1 | 0   |

| 1 | 1 | 0   | 0 | 0 | 0   |

### 5.3 Boolean Function

A Boolean Function is described by an algebraic expression called Boolean expression which consists of binary variables, the constants 0 and 1, and the logic operation symbols.

The function F is equal to 1 if x is 1 or if both y' and z are equal to 1, F is equal to 0 otherwise. Saying y'=1 is equivalent to saying that y=0.

So F is equal to 1 if x=1 or if yz=01.

#### **Truth Table**

The relationship between a function in a truth table and its binary variables can be represented in a truth table.

There are eight possible combination for assigning bits to the three variables x, y and z.

# **Logic Diagrams and Expressions**

| Tru | uth Table                                                          | Logic Equation |

|-----|--------------------------------------------------------------------|----------------|

| XYZ | $\mathbf{F} = \mathbf{X} + \overline{\mathbf{Y}} \cdot \mathbf{Z}$ |                |

| 000 | 0                                                                  | F = X + Y Z    |

| 001 | 1                                                                  |                |

| 010 | 0                                                                  | Logic Diagram  |

| 011 | 0                                                                  | X              |

| 100 | 1                                                                  | 7 - 4          |

| 101 | 1                                                                  |                |

| 110 | 1                                                                  | z              |

| 111 | 1                                                                  |                |

Boolean equations, truth tables and logic diagrams describe the same function!

# 5.4 Integrated Circuits

An IC is a collection of electronic components – resistors, transistors, capacitors, etc. – all stuffed into a tiny chip, and connected together.

Digital ICs and these are designed by using multiple numbers of digital logic gates, multiplexers, flip flops and other electronic components of circuits.

The various gates are interconnected inside the chip to form the required circuit. The chip is mounted in a ceramic or plastic container, and connections are welded by thin gold wires to external pins to form the integrated circuit.

The number of pins may range from 14 in a small IC package to 100 or more in a larger package.

#### **Classification of ICs (Integrated Circuits)**

Below is the classification of different types of ICs basis on their chip size.

- SSI: Small scale integration. 3 30 gates per chip.

- MSI: Medium scale integration. 30 300 gates per chip.

- LSI: Large scale integration. 300 3,000 gates per chip.

- VLSI: Very large scale integration. More than 3,000 gates per chip.

An IC can be further classified as being digital, analog or a combination of both. The most common example of a modern IC is the computer processor, which consists of billions of fabricated transistors, logic gates and other digital circuitry.

The circuit technology is referred as a digital logic family. Each logic family has its own basic electronic circuit.

There are many different logic families of integrated circuit following are popular among them.

#### 1. TTL (transistor-to-transistor logic)

Transistor-transistor logic (TTL) is a class of integrated circuits which maintain logic states and achieve switching with the help of bipolar transistors. Many TTL logic gate s are typically fabricated onto a single integrated circuit (IC).

TTL integrated circuits (ICs) were widely used in applications such as computers, industrial controls, test equipment and instrumentation

A TTL device employs transistor s with multiple emitters in gates having more than one input. Transistor-transistor logic is one of the reasons that integrated circuits are so widely used, as they are less expensive, more reliable and faster

There are different sub-categories or families for transistor-transistor logic, such as:

- Standard transistor-transistor logic

- Fast transistor-transistor logic

- Schottky transistor-transistor logic

- High power transistor-transistor logic

- Low power transistor-transistor logic

- Advanced Schottky transistor-transistor logic

#### 2. ECL(Emitter-coupled logic)

emitter-coupled logic (ECL) is a high-speed integrated circuit

ECL is used in systems such as supercomputers where high speed is essential.

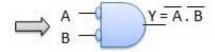

#### 3. MOS(Metal Oxide Semiconductor)

MOS is a method of creating transistors. MOS consists of three layers, a metal conductor, insulating silicon layer, and a semiconductor silicon layer.

#### 4. CMOS

CMOS stands for "Complementary Metal-Oxide-Semiconductor." It's the name of a manufacturing process used to create processors, RAM, and digital logic circuits, and is also the name for chips created using that process.

CMOS is an on-board, battery powered semiconductor chip inside computers that stores information. This information ranges from the system time and date to system hardware settings for your computer.

When you make changes to your BIOS configuration, the settings are not stored on the BIOS chip itself. Instead, they are stored on a special memory chip, which is referred to as "the CMOS."

The picture shows an example of the most common CMOS coin cell battery (Panasonic CR 2032 3V) used to power the CMOS memory.

### 5.5 Combinational circuits

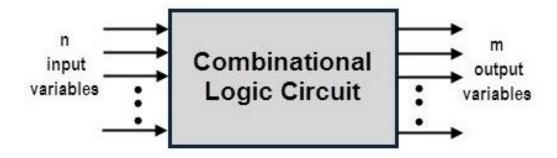

A combinational circuit is a connected arrangement of logic gates with set of inputs and outputs.

A combinational circuit comprises of input variables, logic gates and output variables. The logic gates accepts the inputs and depending on the type of functioning of the logic gate, output signals are generated from them.

Diagram below shows the combinational circuit having n inputs and m outputs.

The n number of inputs shows that there are 2<sup>n</sup> possible combinations of bits at the input. Therefore, the output is expressed in terms m Boolean expressions.

#### Implementation steps

- Identify the input and output variables.

- Determine the relation between the input and output variables.

- Construct truth table according to input output specifications.

- Find out the Boolean expressions for outputs in terms of inputs.

- Minimize the Boolean expressions.

- The logic diagram is drawn.

#### 1. Half Adder

With the help of half adder, we can design circuits that are capable of performing simple addition with the help of logic gates.

The half adder circuit has two inputs: A and B, which add two input digits and generate a carry and sum.

#### **Block Diagram**

#### **Truth Table**

| INP | UTS | OUTPUTS |       |  |

|-----|-----|---------|-------|--|

| A   | В   | SUM     | CARRY |  |

| 0   | 0   | 0       | 0     |  |

| 0   | 1   | 1       | 0     |  |

| 1   | 0   | 1       | 0     |  |

| 1   | 1   | 0       | 1     |  |

1-bit adder can be easily implemented with the help of the XOR Gate for the output 'SUM' and an AND Gate for the 'Carry'.

When we need to add, two 8-bit bytes together, we can be done with the help of a full-adder logic.

$$\mathbf{Sum} = \overline{\mathbf{A}} \cdot \mathbf{B} + \mathbf{A} \cdot \overline{\mathbf{B}}$$

$$\mathbf{Carry} = \mathbf{A} \cdot \mathbf{B}$$

#### Circuit

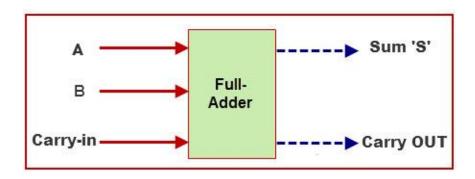

#### 2. Full Adder

A full-adder has three inputs and two outputs

The first two inputs are A and B and the third input is an input carry as C-IN. The output carry is designated as C-OUT and the normal output is designated as S.

#### **Block Diagram**

#### **Truth Table**

| 9 | INPUTS | OUTPUT |       |   |

|---|--------|--------|-------|---|

| A | В      | C-IN   | C-OUT | S |

| 0 | 0      | 0      | 0     | 0 |

| 0 | 0      | 1      | 0     | 1 |

| 0 | 1      | 0      | 0     | 1 |

| 0 | 1      | 1      | 1     | 0 |

| 1 | 0      | 0      | 0     | 1 |

| 1 | 0      | 1      | 1     | 0 |

| 1 | 1      | 0      | 1     | 0 |

| 1 | 1      | 1      | 1     | 1 |

So, we can implement a full adder circuit with the help of two half adder circuits. At first, half adder will be used to add A and B to produce a partial Sum and a second half adder logic can be used to add C-IN to the Sum produced by the first half adder to get the final S output.

### **Full Adder Logic Circuit**

# 5.6 Flip-Flops

A flip-flop is a type of circuit that contains two states, 0 or 1(on or off and are often used to store state information. By sending a signal to the flip-flop, the state can be changed.

Flip-flops are used in a number of electronics, including computers and communications equipment. Flip-flop circuits are interconnected to form the logic gates for the digital integrated circuits (IC s) used in memory chips and microprocessors.

There are several different kinds of flip-flop circuits, with designators such as T (toggle), S-R (set/reset), J-K and D (data).

A flip-flop typically includes zero, one, or two input signals as well as a clock signal and an output signal. Some flip-flops also include a clear input signal to reset the current output.

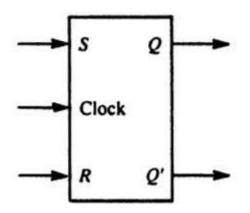

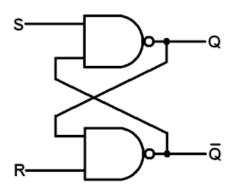

#### **SR Flip Flop**

SR flip-flop is one of the most common types of flip-flop. SR stands for Set Reset.

Diagram shows the graphic symbol of SR flip-flop. The flip-flop has three inputs S (set), R, (reset) and C (clock)

| S | R | Q             |

|---|---|---------------|

| 0 | 0 | No change     |

| 0 | 1 | 0             |

| 1 | 0 | 1             |

| 1 | 1 | Indeterminate |

#### **Operation of SR flipflop**

If there is no signal at the clock input C, the output of the circuit cannot change the values of S and R.

If S=1 and R=0 when C changes from 0 to 1, output Q is set to 1.

If S=0 and R=1 when C changes from 0 to 1, output Q is cleared to 0.

If both S and R are 0 during the clock transition, the output does not change.

When both S and R are equal to 1, the output is unpredictable and may go to either 0 or 1.

#### **Logic Diagram**

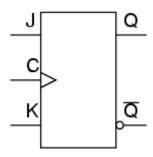

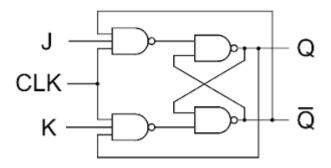

#### JK flip Flop

The JK Flip Flop is the most widely used flip flop. It is considered to be a universal flip-flop circuit. The sequential operation of the JK Flip Flop is same as for the RS flip-flop with the same SET and RESET input.

# The JK Flip Flop name has been kept on the inventor name of the circuit known as Jack Kilby.

The intermediate condition of SR flip-flop is defined in JK.

| Truth Table |   |     |                            |  |  |  |  |

|-------------|---|-----|----------------------------|--|--|--|--|

| J           | Κ | CLK | Q                          |  |  |  |  |

| 0           | 0 | t   | Q <sub>n</sub> (no change) |  |  |  |  |

| 1           | 0 | †   | 1                          |  |  |  |  |

| 0           | 1 | t   | 0                          |  |  |  |  |

| 1           | 1 | †   | $\overline{Q}_0$ (toggles) |  |  |  |  |

#### Operation of JK flipflop

The J input is equivalent to the S (set) input of SR flip-flop and K input is equivalent to R (clear) input.

Instead of indeterminate condition, the JK flip-flop has a complement condition (toggle).

#### **Logic Diagram**

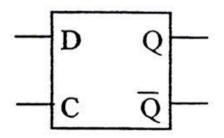

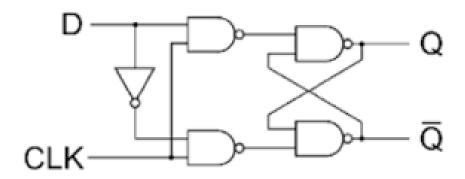

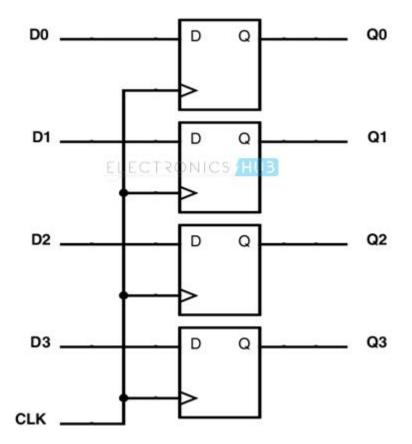

#### D Flip-flop

The D-type flip-flop is constructed from a gated SR flip-flop with an inverter added between the S and the R inputs to allow for a single D (data) input.

The D Flip Flop is by far the most important of the clocked flip-flops as it ensures that ensures that inputs S and R are never equal to one at the same time.

|       | Circuit     |

|-------|-------------|

| Input | Action      |

| D     | $Q_{(1+1)}$ |

| 0     | 0           |

| 1     | 1           |

Simply, for positive transition on clock signal,

If  $D = 0 \Rightarrow Q = 0$  so flip flop is reset.

If  $D = 1 \Rightarrow Q = 1$  so flip flop is set.

### **Operation of D flip-flop**

➤ If the clock signal is high (rising edge to be more precise) and if D input is high, then the output is also high and if D input is low, then the output will become low.

#### **Logic Diagram**

# 5.7 | Summary

In this chapter you have learned about:

- Logic Gates

- Boolean Algebra

- Boolean Function

- Integrated Circuit

- Combinational Circuit

- Flip-flops

# **Unit 6: Components Of Digital Computer**

### **Unit Structure**

- 6.1. Encoder

- 6.2. Decoder

- 6.3. Multiplexer

- 6.4. Registers

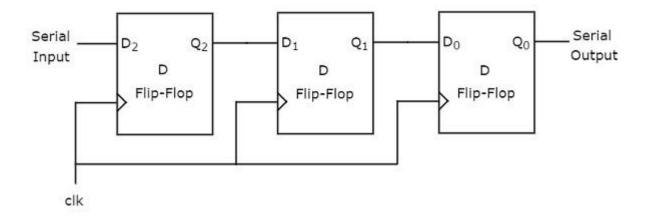

- 6.5. Shift Registers

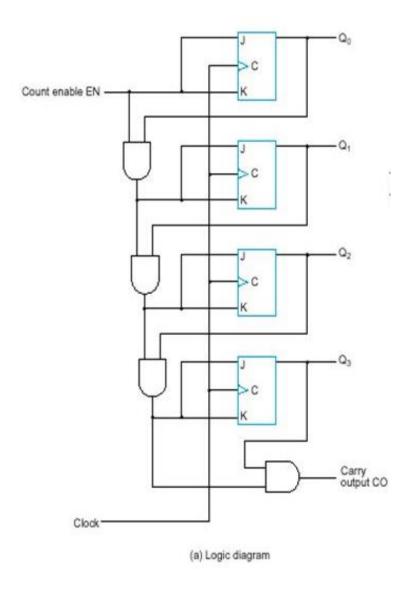

- 6.6. Binary Counters

- 6.7. Summary

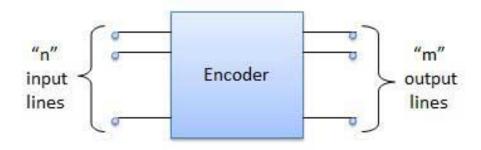

# 6.1 Encoder

Encoder is a combinational circuit which is designed to perform the inverse operation of the decoder.

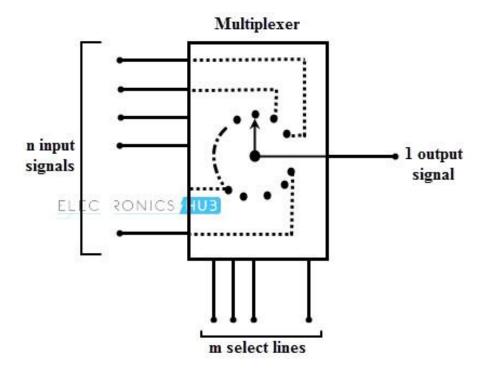

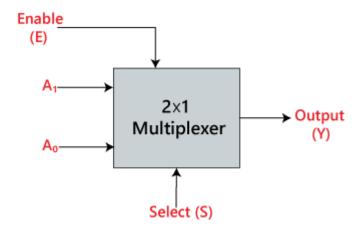

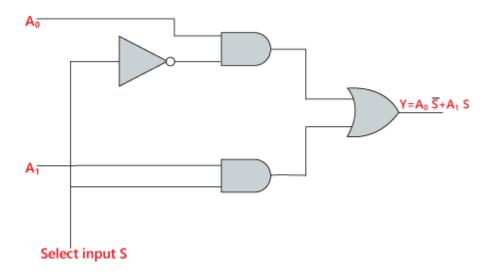

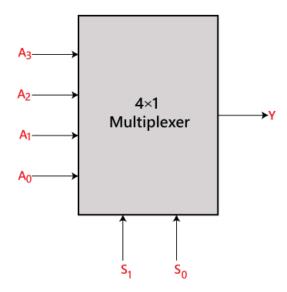

An encoder has n number of input lines and m number of output lines.

An encoder produces an m bit binary code corresponding to the digital input number. The encoder accepts an n input digital word and converts it into an m bit another digital word.

#### **Block diagram**

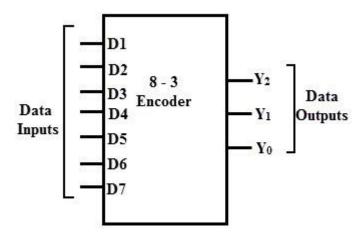

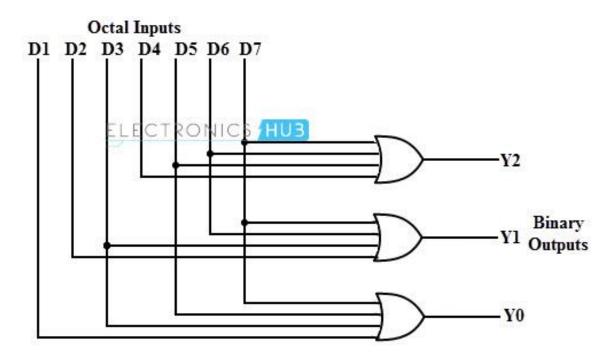

#### **Octal to Binary Encoder**

#### **Block Diagram**

An octal to binary encoder has 8 input lines D0 to D7 and 3 output lines Y0 to Y2.

#### Truth table

|                       | Inputs         |                |                |                |                |                |                |                | utpu           | ts             |

|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

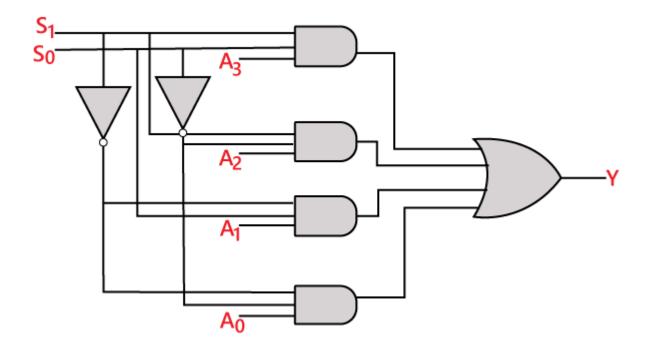

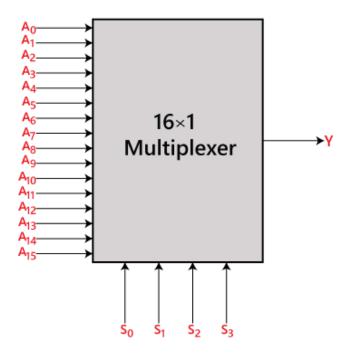

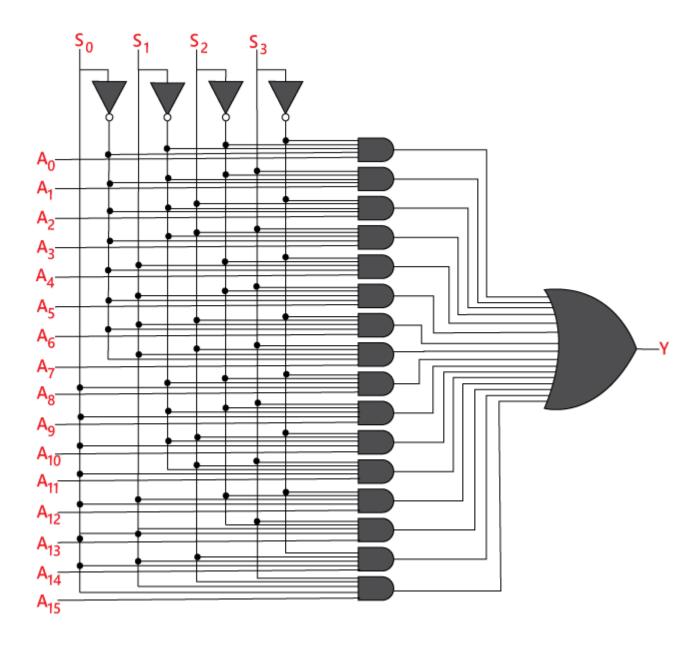

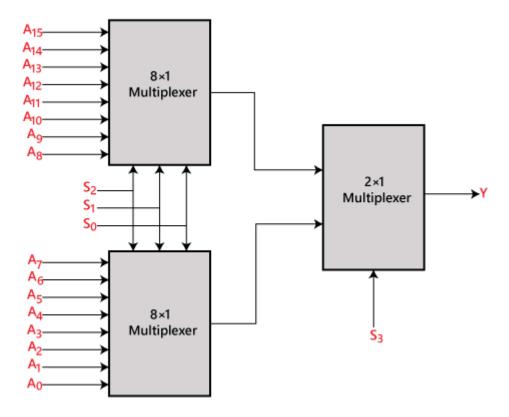

| <b>D</b> <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | $\mathbf{D}_4$ | D <sub>3</sub> | D <sub>2</sub> | $\mathbf{D}_1$ | $\mathbf{D}_0$ | Y <sub>2</sub> | $\mathbf{Y}_1$ | $\mathbf{Y}_0$ |